Transistor de ensambladura bipolar

BJT vuelve a dirigir aquí. Para la prueba japonesa del conocimiento de idiomas, vea Prueba japonesa de la habilidad del negocio.

A transistor de ensambladura bipolar (BJT) es un tipo de transistor. Es un dispositivo del tres-terminal construido de dopado semiconductor el material y se puede utilizar adentro el amplificar o usos de la conmutación. Los transistores bipolares son así que nombrado porque su operación implica ambos electrones y agujeros.

Aunque una parte pequeña de la corriente del transistor es debido al flujo de portadores de mayoría, la mayor parte de la corriente del transistor es debido al flujo de portadores de la minoría y BJTs se clasifica tan como dispositivos del "minoría-portador".

Un transistor de NPN se puede considerar como dos diodos con compartido ánodo región. En la operación típica, la emisor-base ensambladura es polarizado hacia adelante y la ensambladura del base-colector es en polarización negativa reverso. En un transistor de NPN, por ejemplo, cuando un voltaje positivo se aplica a la ensambladura del emisor de base, el equilibrio entre generado terma lportadores y el campo eléctrico de rechazo del región de agotamiento llega a ser desequilibrado, permitiendo que los electrones termal excitados inyecten en la región baja. Estos electrones vagan (o "difuso") a través de la base de la región de la alta concentración cerca del emisor hacia la región de la concentración baja cerca del colector. Los electrones en la base se llaman portadores de la minoría porque es la base dopado p-tipo que haría los agujeros portador de mayoría en la base.

La región baja del transistor se debe hacer fina, de modo que los portadores puedan difundir a través de él en mucho menos tiempo que el curso de la vida del portador de la minoría del semiconductor, para reducir al mínimo el porcentaje de portadores eso recombine antes de alcanzar la ensambladura del collector-base. El grueso de la base debe ser menos que longitud de difusión de los electrones. La ensambladura del collector-base es reverse-biased, así que poca inyección del electrón ocurre del colector a la base, pero de los electrones que difuso a través de la base hacia el colector son barridos en el colector por el campo eléctrico en la región de agotamiento de la ensambladura del collector-base.

Voltaje, corriente, y control de la carga

La corriente del collector-emitter se puede ver como siendo controlado por la corriente del emisor de base (control actual), o por el voltaje del emisor de base (control del voltaje). Estas opiniónes son relacionadas por la relación current-voltage de la ensambladura del emisor de base, que es justa la curva current-voltage exponencial generalmente de a ensambladura del p-n (diodo).

La explicación física para la corriente de colector es la cantidad de carga del minoría-portador en la región baja. Los modelos detallados de la acción del transistor, tales como el modelo de Gummel-Poon, explican la distribución de esta carga explícitamente para explicar comportamiento del transistor más exactamente. La opinión del cargar-control maneja fácilmente los fototransistores, del donde los portadores de la minoría en la región baja son creados por la absorción fotones, y manijas la dinámica del tiempo turn-off, o de la recuperación, que depende de carga en la recombinación baja de la región. Sin embargo, puesto que la carga baja no es una señal que es visible en los terminales, las opiniones de la corriente y del voltaje-control se utilizan generalmente en diseño y análisis de circuito.

En circuito análogo diseñe, la opinión del actual-control se utiliza a veces puesto que es aproximadamente linear. Es decir, la corriente de colector está aproximadamente βF mide el tiempo de la corriente de la base. Algunos circuitos básicos pueden ser diseñados si se asume que el voltaje de la emisor-base es aproximadamente constante, y que la corriente de colector es épocas beta la corriente de la base. Sin embargo, diseñe a exactamente y confiablemente los circuitos del bjt de la producción, el modelo del voltaje-control (por ejemplo, Ebers-Moll) se requiere. El modelo del voltaje-control requiere una función exponencial considerado, pero cuando se lineariza tales que el transistor se puede modelar como transconductancia, como en el modelo de Ebers-Moll, el diseño para los circuitos tales como amplificadores diferenciados se convierte en otra vez un problema sobre todo linear, así que la opinión del voltaje-control se prefiere a menudo. Para circuitos translinear, en que la curva exponencial del intravenoso es dominante a la operación, los transistores se modelan generalmente como voltaje controlado con la transconductancia proporcional a la corriente de colector. El diseño de circuito llano del transistor es generalmente el usar realizado ESPECIA o un simulador análogo comparable del circuito, así que la complejidad del modelo no está generalmente de mucha preocupación al diseñador.

Transistor "alfa" y "beta"

La proporción de electrones capaces de cruzar la base y de alcanzar el colector es una medida de la eficacia de BJT. El doping pesado de la región del emisor y doping ligero de la causa baja de la región muchos más electrones que se inyectarán del emisor en la base que los agujeros que se inyectarán de la base en el emisor. común-emisor aumento actual se representa cerca βF o hFE. Es aproximadamente el cociente de la corriente de colector de la C.C. a la corriente baja de la C.C. en la región delantero-activa, y es 100 típicamente mayor que. Otro parámetro importante es común-base aumento actual, αF. El aumento actual de la común-base es aproximadamente el aumento de la corriente del emisor al colector en la región delantero-activa. Este cociente tiene generalmente un valor cerca de la unidad; entre 0.98 y 0.998. La alfa y beta son relacionadas más exacto por las identidades siguientes (transistor de NPN):

Estructura

Un BJT consiste en tres diferentemente dopado regiones de semiconductor, emisor región, base región y colector región. Estas regiones son, respectivamente, p mecanografíe, n mecanografíe y p mecanografíe adentro a PNP, y n mecanografíe, p mecanografíe y n mecanografíe adentro a Transistor de NPN. Cada región de semiconductor está conectada con un terminal, etiquetado apropiadamente: emisor (e), base (b) y colector (c).

base está situado físicamente entre emisor y colector y se hace del material ligeramente dopado, alto de la resistencia. El colector rodea la región del emisor, haciéndolo casi imposible para los electrones inyectados en la región baja para escapar ser recogido, así haciendo el valor que resulta de α muy cerca de la unidad, y por eso, dando al transistor un β grande. Una vista seccionada transversalmente de un BJT indica que la ensambladura del collector-base tiene un área mucho más grande que la ensambladura de la emisor-base.

El transistor de ensambladura bipolar, desemejante de otros transistores, no es generalmente un dispositivo simétrico. Esto significa eso que intercambia el colector y las marcas del emisor la licencia del transistor el modo y el comienzo activos delanteros para funcionar en modo reverso. Porque la estructura interna del transistor se optimiza generalmente a la operación del delantero-modo, intercambiar el colector y el emisor hace los valores de α y de β en la operación reversa mucho más pequeña que ésas encontradas en la operación delantera; el α del modo reverso es a menudo más bajo de 0.5. La carencia de la simetría es sobre todo debido a los cocientes de doping del emisor y del colector. El emisor se dopa pesadamente, mientras que el colector se dopa ligeramente, permitiendo que un voltaje de polarización reversa grande sea aplicado antes de que la ensambladura del collector-base analice. La ensambladura del collector-base es en polarización negativa reverso en la operación normal. La razón que el emisor se dopa pesadamente es aumentar la eficacia de inyección del emisor: el cociente de los portadores inyectados por el emisor a ésos inyectado por la base. Para el aumento de gran intensidad, la mayor parte de los portadores inyectados en la ensambladura de la emisor-base deben venir del emisor.

Los transistores bipolares "laterales" de resultado inferior usados a veces adentro Cmos los procesos se diseñan a veces simétricamente, es decir, sin diferencia entre la operación delantera y posterior.

Los cambios pequeños en el voltaje aplicaron a través de las causas de los terminales del emisor de base la corriente que fluye entreemisor y colector para cambiar perceptiblemente. Este efecto se puede utilizar para amplificar el voltaje o la corriente de entrada. BJTs se puede pensar en como voltaje-controlada fuentes actuales, pero se caracterizan más simplemente como fuentes actuales actual-controladas, o amplificadores actuales, debido a la impedancia baja en la base.

Los transistores tempranos fueron hechos de germanio pero la mayoría del BJTs moderno se hace de silicio. Ahora hacen una minoría significativa también de arseniuro de galio, especialmente para los usos muy de alta velocidad.

NPN

NPN es uno de los dos tipos de transistores bipolares, en los cuales las letras "N" y "P" refieren a la mayoría portadores de la cargadentro de las diversas regiones del transistor. La mayoría de los transistores bipolares usados hoy son NPN, porque movilidad de electrón es más alto que movilidad de agujero en semiconductores, permitiendo mayores corrientes y una operación más rápida.

Los transistores de NPN consisten en una capa del p dopado el semiconductor (la "base") entre dos N-dopó capas. Una corriente pequeña que incorpora la base en modo del común-emisor se amplifica en la salida del colector. En otros términos, un transistor de NPN es "ON" cuando se tira su base alto concerniente al emisor.

La flecha en el símbolo del transistor de NPN está en la pierna y los puntos del emisor en la dirección del corriente convencional fluya cuando el dispositivo está en modo activo delantero.

Uno mnemónica el dispositivo para identificar el símbolo para el transistor de NPN es "not pi ointingn".

PNP

El otro tipo de BJT es el PNP con las letras "P" y "N" que refiere a la mayoría portadores de la carga dentro de las diversas regiones del transistor.

Los transistores de PNP consisten en una capa de n dopado semiconductor entre dos capas de material P-dopado. Una corriente pequeña que deja la base en modo del común-emisor se amplifica en la salida del colector. En otros términos, un transistor de PNP es "ON" cuando se tira su base bajo concerniente al emisor.

La flecha en el símbolo del transistor de PNP está en la pierna y los puntos del emisor en la dirección del corriente convencional fluya cuando el dispositivo está en modo activo delantero.

Un dispositivo mnemónico para identificar el símbolo para el transistor de PNP es "points in proudly ".

Transistor bipolar del Heterojunction

transistor bipolar del heterojunction (HBT) es una mejora del BJT que puede manejar señales mismo de de alta frecuencia hasta varios cientos Gigahertz. Es común hoy en día en los circuitos ultrarrápidos, sobre todo sistemas del RF. Los transistores del Heterojunction tienen diversos semiconductores para los elementos del transistor. El emisor se compone generalmente de un material más grande del bandgap que la base. La figura demuestra que esta diferencia en bandgap permite que la barrera para que los agujeros inyecten al revés en la base, denotada en figura como Δφp, ser hecho grande, mientras que la barrera para que electrones inyecten en el Δφ bajon se hace punto bajo. Las ayudas de este arreglo de la barrera reducen la inyección de portador de la minoría de la base cuando es la ensambladura de la emisor-base debajo polariza, y reduce así actual hacia adelante bajo y aumenta eficacia de inyección del emisor.

La inyección mejorada de portadores en la base permite que la base tenga un nivel de doping más alto, dando por resultado una resistencia más baja para tener acceso al electrodo bajo. En el BJT más tradicional, también designado el homojunction BJT, la eficacia de la inyección de portador del emisor a la base es determinada sobre todo por el cociente de doping entre el emisor y la base, que significa que la base se debe dopar ligeramente para obtener la alta eficacia de inyección, haciendo su resistencia relativamente alta. Además, más arriba el doping en la base puede mejorar figuras del mérito como Voltaje temprano disminuyendo enangostar de la base.

El calificar de la composición en la base, por ejemplo, progresivamente aumentando la cantidad de germanio en a SiGe transistor, causas un gradiente en bandgap en la base neutral, denotada en la figura por ΔφG, proporcionando un campo "incorporado" que asiste a transporte del electrón a través de la base. Eso componente de la deriva de las ayudas de transporte el transporte difusivo normal, aumentando la respuesta de frecuencia del transistor acortando el tiempo del tránsito a través de la base.

Dos HBTs de uso general son arseniuro de galio del silicio-germanio y del aluminio, aunque una variedad amplia de semiconductores se puede utilizar para la estructura de HBT. Las estructuras de HBT se crecen generalmente cerca epitaxy las técnicas tienen gusto MOCVD y MBE.

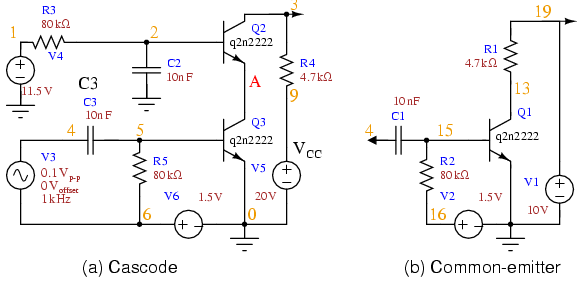

Transistores en circuitos

El diagrama enfrente de es una representación esquemática de un transistor del npn conectado con dos fuentes del voltaje. Para hacer que el transistor conduce la corriente apreciable (en la orden de 1 mA) C a E, VBE debe estar sobre un valor mínimo designado a veces voltaje del cut-in. El voltaje del cut-in es generalmente cerca de 600 milivoltios para el silicio BJTs, pero puede ser diferente dependiendo del nivel actual seleccionado para el uso y el tipo de transistor. Este voltaje aplicado causa la ensambladura más baja del p-n al "excitamiento" que permite un flujo de electrones del emisor en la base. Debido a el campo eléctrico que existe entre la base y el colector (causados cerca VCE), la mayoría de estos electrones cruza la ensambladura superior del p-n en el colector para formar la corriente de colector, IC. El resto de los electrones recombina con los agujeros, los portadores de mayoría en la base, haciendo una corriente a través de la conexión baja para formar la corriente baja, IB . Según las indicaciones del diagrama, la corriente del emisor, IE, es la corriente total del transistor que es la suma de las otras corrientes terminales. Eso es:

En el diagrama, las flechas que representan el punto actual en la dirección del eléctrico o corriente convencional- el flujo de electrones está en la dirección opuesta de las flechas puesto que los electrones llevan la negativa carga eléctrica. El cociente de la corriente de colector a la corriente baja se llama Aumento actual de C.C.. Este aumento es generalmente absolutamente grande y es a menudo 100 o más.

Debe también ser observado que la corriente del emisor está relacionada con VBE exponencial. En la temperatura ambiente, aumentando VBE en cerca de 60 milivoltios aumenta la corriente del emisor en un factor de 10. La corriente baja es aproximadamente proporcional a la corriente del emisor, así que varía la misma manera.

Regiones de la operación

Los transistores bipolares tienen cinco regiones distintas de la operación, definidas sobre todo por diagonal aplicado:

- Delantero-activo (o simplemente, activo): Se polariza hacia adelante la ensambladura de la emisor-base y la ensambladura del base-colector es en polarización negativa reverso. La mayoría de los transistores bipolares se diseñan para producir el aumento actual del común-emisor más grande, βf, en modo delantero-activo. Si éste es el caso, la corriente del collector-emitter está aproximadamente proporcional la corriente baja, pero muchas veces a más grande, para las variaciones actuales bajas pequeñas.

- Reverso-activo (o inverso-activo o invertido): Invirtiendo las condiciones que predisponen de la región delantero-activa, un transistor bipolar entra modo reverso-activo. En este modo, las regiones del emisor y de colector cambian papeles. Puesto que la mayoría del BJTs se diseña para maximizar aumento actual en el modo delantero-activo, βf en modo invertido está varias (2 - 3 para el transistor ordinario del germanio) veces más pequeño. Este modo del transistor se utiliza raramente, generalmente siendo considerado solamente para las condiciones de seguridad y algunos tipos de lógica bipolar. El voltaje de interrupción del diagonal reverso a la base puede ser una orden de la magnitud más bajo en esta región.

- Saturación: Con ambas ensambladuras forward-biased, un BJT está en modo de la saturación y facilita la conducción de gran intensidad del emisor al colector. Este modo corresponde a "ON" lógico, o a un interruptor cerrado.

- Atajo: En el atajo, predisponiendo el contrario de las condiciones de la saturación (revés de ambas ensambladuras predispuesto) esté presente. Hay el flujo muy poco actual, que corresponde a "OFF" lógico, o un interruptor abierto.

- Interrupción de la avalancha región

Mientras que estas regiones están bien definidas para el voltaje aplicado suficientemente grande, se traslapan algo para (menos que algunos cientos milivoltios) los diagonales pequeños. Por ejemplo, en la configuración típica del poner a tierra-emisor de un NPN BJT usado como interruptor del pulldown en lógica digital, el estado de "OFF" nunca implica una ensambladura reverse-biased porque nunca va el voltaje bajo bajo tierra; sin embargo el polarizar hacia adelante está bastante cercano a cero que esencialmente fluya ninguna corriente, así que este final de la región activa delantera se puede mirar como la región del atajo.

Historia

(Punto-entre en contacto con) el transistor bipolar era inventado en diciembre de 1947 en Laboratorios del teléfono de Bell por Juan Bardeen y Walter Brattain bajo dirección de Guillermo Shockley. La versión de la ensambladura, inventado por Shockley en 1948, gozado tres décadas como el dispositivo de la opción en el diseño de discreto y circuitos integrados. Hoy en día, el uso del BJT ha declinado a favor de Cmos tecnología en el diseño de circuitos integrados digitales.

Transistores del germanio

germanio el transistor era más común en los años 50 y los años 60, y mientras que exhibe un voltaje "cortado" más bajo, la fabricación de él más conveniente para algunos usos, él también tiene una mayor tendencia a exhibir fugitivo termal.

Técnicas de fabricación tempranas

Los varios métodos de fabricar los transistores de ensambladura bipolar fueron desarrollados.

- Transistor de ensambladura crecido - primer tipo de transistor de ensambladura bipolar hecho. Inventado cerca Guillermo Shockley en Laboratorios de Bell. Inventado encendido 23 de junio, 1948. Patente archivada encendido 26 de junio, 1948.

- Transistor de ensambladura de aleación - granos de la aleación del emisor y del colector fundidos a la base. Convertido enGeneral electric y RCA en 1951.

- Transistor micro de la aleación - tipo de alta velocidad de transistor de ensambladura de aleación. Convertido en Philco.

- Transistor difundido aleación micro - tipo de alta velocidad de transistor de ensambladura de aleación. Convertido en Philco.

- Transistor difundido aleación del poste - tipo de alta velocidad de transistor de ensambladura de aleación. Convertido en Philips.

- Transistor del tetrodo - variante de alta velocidad del transistor de ensambladura crecido o transistor de ensambladura de aleación con dos conexiones a la base.

- Transistor de la barrera superficial - transistor de ensambladura de alta velocidad de la barrera del metal. Convertido en Philco en 1953.

- Transistor del Drift-field - transistor de ensambladura bipolar de alta velocidad. Inventado cerca Herberto Kroemer en la oficina central de la tecnología de las telecomunicaciones del servicio postal alemán, adentro 1953.

- Transistor de la difusión - tipo moderno transistor de ensambladura bipolar. Prototipos convertido en los laboratorios de Bell adentro 1954.

- Transistor bajo difundido - primera puesta en práctica del transistor de la difusión.

- Transistor del Mesa - Convertido en Texas Instruments en 1957.

- Transistor Planar - el transistor de ensambladura bipolar que hizo monolítico producido en serie circuitos integrados posible. Convertido por el Dr. Jean Hoerni en Fairchild en 1959.

- Transistor Epitaxial - un transistor de ensambladura bipolar hecho usando la deposición de la fase del vapor. Vea epitaxy. Permite el control muy exacto de dopar niveles y gradientes.

Teoría y el modelar

En la discusión abajo, el foco está en el transistor bipolar del npn. En npn el transistor en se llama qué modo activo el voltaje del emisor de base VSEA y voltaje de collector-base VCBES es el positivo, polarizando la ensambladura de la emisor-base hacia adelante y reverso-predisponiendo la ensambladura del collector-base. En el modo de operación activo, los electrones se inyectan del n-tipo polarizado hacia adelante región del emisor en el p-tipo base adonde difunden al n-tipo en polarización negativa reverso colector y son barridos lejos por el campo eléctrico en la ensambladura en polarización negativa reversa del collector-base. Para una figura que describe diagonal delantero y reverso, vea el extremo del artículo diodos del semiconductor.

modelos de la Grande-señal

Modelo de Ebers-Moll

Las corrientes del emisor y de colector de la C.C. en modo activo son modeladas bien por una aproximación al modelo de Ebers-Moll:

La corriente interna baja está principalmente por la difusión y donde

- VT es voltaje termal kT/q (aproximadamente 26 milivoltios en la temperatura ambiente del ≈ de 300 K).

- IE es la corriente del emisor

- IC es la corriente de colector

- αT es el aumento actual del cortocircuito delantero de la base común (0.98 a 0.998)

- IES es la corriente reversa de la saturación del diodo del emisor de base (en la orden de 10−15 a 10−12 amperios)

- VSEA es el voltaje del emisor de base

- Dn es la constante de difusión para los electrones en el p-tipo base

- W es la anchura baja

La corriente de colector es levemente menos que la corriente del emisor, desde el valor de αT está muy cerca de 1.0. En el BJT a la cantidad pequeña de corriente del emisor de base causa una cantidad más grande de corriente del collector-emitter. El cociente de la corriente permitida del collector-emitter a la corriente del emisor de base se llama aumento actual, β o hFE. Un valor del β de 100 es típico para los transistores bipolares pequeños. En una configuración típica, una corriente muy pequeña de la señal atraviesa la ensambladura del emisor de base para controlar la corriente del emisor-colector. el β se relaciona con el α con las relaciones siguientes:

Eficacia del emisor: ; es decir, el cociente de la corriente inyectado en la base a la corriente en el emisor; los dos diferencian debido a la inyección posterior de la base en el emisor y a la recombinación. Vea generación de portador y recombinación.

Unapproximated las ecuaciones de Ebers-Moll usadas para describir las tres corrientes en cualquier región de funcionamiento se dan abajo. Estas ecuaciones se basan en el modelo del transporte para un transistor de ensambladura bipolar. Vea, por ejemplo, a Sedra y a Smith.

donde

- iC es la corriente de colector

- iB es la corriente de la base

- iE es la corriente del emisor

- βF es el aumento actual del emisor común delantero (20 a 500)

- βR es el aumento actual del emisor común reverso (0 a 20)

- IS es la corriente reversa de la saturación (en la orden de 10−15 a 10−12 amperios)

- VT es voltaje termal (aproximadamente 26 milivoltios en la temperatura ambiente del ≈ de 300 K).

- VSEA es el voltaje del emisor de base

- VA.C. es el voltaje del base-colector

modulación de la Base-anchura

- Artículo principal: Efecto temprano

Como el voltaje de collector-base aplicado (VBC) varía, la región de agotamiento del collector-base varía de tamaño. Un aumento en el voltaje de collector-base, por ejemplo, causa un mayor diagonal reverso a través de la ensambladura del collector-base, aumentando la anchura de la región de agotamiento del collector-base, y disminuyendo la anchura de la base. Esta variación en anchura baja a menudo se llama "Efecto temprano" después de su descubridor James M. Temprano.

El enangostar de la anchura baja tiene dos consecuencias:

- Hay una poca ocasión para la recombinación dentro de la región baja "más pequeña".

- El gradiente de la carga se aumenta a través de la base, y por lo tanto, la corriente de los portadores de la minoría inyectados a través de los aumentos de la ensambladura del emisor.

Ambos factores aumentan el colector o "haga salir" la corriente del transistor en respuesta a un aumento en el voltaje de collector-base.

En región activa delantera el efecto temprano modifica la corriente de colector (iC) y el aumento actual del emisor común delantero (βF) según lo dado por las ecuaciones siguientes:

Donde

- VCBES es el voltaje de collector-base

- VA es el voltaje temprano (15 V a 150 V)

- βF0 es el aumento actual del común-emisor delantero cuando VCB = 0 V

Características current-voltage

Las asunciones siguientes están implicadas al derivar las características current-voltage ideales del BJT.

- Inyección del nivel bajo

- Doping uniforme en cada región con las ensambladuras precipitadas

- Flujo actual unidimensional

- Recombinación-generación insignificante en regiones de carga de espacio

- Campos eléctricos insignificantes fuera de regiones de carga de espacio.

Es importante caracterizar las corrientes de difusión de la minoría inducidas por la inyección de portadores.

Con respecto al diodo de ensambladura del pn, una relación dominante es la ecuación de la difusión.

Una solución de esta ecuación está abajo, y dos condiciones de límite se utilizan para solucionar y para encontrar C1 y C2.

Las ecuaciones siguientes se aplican a la región del emisor y de colector, respectivamente, y a los orígenes 0, 0', y 0'' apliqúese a la base, al colector, y al emisor.

Una condición de límite del emisor está abajo:

Los valores de las constantes A1 y B1 es cero debido a las condiciones siguientes de las regiones del emisor y de colector como y .

Desde entonces A1 = B1 = 0, los valores de ΔnE(0'') y Δnc(0') sea A2 y B2, respectivamente.

Expresiones de IEn y ICn puede ser evaluado.

Puesto que ocurre la recombinación insignificante, el segundo derivado de ΔpB(x) es cero. Hay por lo tanto una relación linear entre exceso de densidad del agujero y x.

Los siguientes son condiciones de límite de ΔpB.

Substituya en la relación linear antedicha.

- .

Con este resultado, derive el valor de IEp.

Utilice las expresiones de IEp, IEn, ΔpB(0), y ΔpB(W) para desarrollar una expresión de la corriente del emisor.

Semejantemente, una expresión de la corriente de colector se deriva.

Una expresión de la corriente baja se encuentra con los resultados anteriores.

Punchthrough

Cuando el voltaje del base-colector alcanza cierto (valor del específico del dispositivo), el límite de la región de agotamiento del base-colector resuelve el límite de la región de agotamiento del emisor de base. Cuando en este estado el transistor no tiene con eficacia ninguna base. El dispositivo pierde así todo el aumento cuando en este estado.

Modelo del cargar-control de Gummel-Poon

Modelo de Gummel-Poon es un modelo cargar-controlado detallado de la dinámica de BJT, que ha sido adoptada y elaborada por otras para explicar dinámica del transistor en mayor detalle que lo hacen los modelos terminal-basados típicamente. Este modelo también incluye la dependencia del transistor β- valores sobre los niveles actuales de la C.C. en el transistor, que son actual-independiente asumida en el modelo de Ebers-Moll. Vea, por ejemplo, a Sedra y a Smith.

Modelos Small-signal

modelo del h-parámetro

Otro de uso general modelo para analizar los circuitos de BJT es "h-parámetro" modelo, de cerca relacionado a modelo híbrido-pi y y-parámetro two-port, pero usar la corriente de la entrada y el voltaje de la salida como variables independientes, más bien que entró e hizo salir voltajes. Esta red two-port se satisface particularmente a BJTs como se presta fácilmente al análisis del comportamiento del circuito, y se puede utilizar desarrollar otros modelos exactos. Como se muestra, el término "x" en el modelo representa el plomo de BJT dependiendo de la topología usada. Para el modo del común-emisor los varios símbolos adquieren los valores específicos como -

- x = "e" puesto que es una topología del común-emisor

- Terminal 1 = base

- Terminal 2 = colector

- Terminal 3 = emisor

- ien = corriente de la base (ib)

- io = corriente de colector (ic)

- Ven = voltaje del Base-a-emisor (VSEA)

- Vo = voltaje del Colector-a-emisor (VCE)

y los h-parámetros se dan cerca -

- hIX = hIE - La impedancia de la entrada del transistor (que corresponde a la resistencia del emisor re).

- hrx = hre - Representa la dependencia del transistor IB–VSEA curva en el valor de VCE. Es generalmente muy pequeño y se descuida a menudo (asumido para ser cero).

- hfx = hFE - Actual-gane del transistor. Este parámetro se especifica a menudo como hFE o la C.C. actual-gana (βC.C.) en datasheets.

- hbuey = hoe - La impedancia de la salida del transistor. Este término se especifica como entrada y tiene que generalmente ser invertido para convertirla a una impedancia.

Como se muestra, los h-parámetros tienen subíndices minúsculos y por lo tanto significan condiciones o análisis de la CA. Para las condiciones de la C.C. se especifican en mayúscula. Para la topología del CE, un modelo aproximado del h-parámetro es de uso general que simplifica más lejos el análisis del circuito. Para esto hoe y hre se descuidan los parámetros (es decir, se fijan al infinito y a cero, respectivamente). Debe también ser observado que el modelo del h-parámetro como se muestra está satisfecho al análisis de baja frecuencia, small-signal. Para los análisis de alta frecuencia las capacitancias del interelectrodo que son importantes en los de alta frecuencia deben ser agregadas.

Usos

El BJT sigue siendo un dispositivo que sobresale en algunos usos, tales como diseño de circuito discreto, debido a la selección muy amplia de los tipos de BJT disponibles, y debido a su colmo transconductancia y resistencia de salida comparada a MOSFETs. El BJT es también la opción para exigir los circuitos análogos, especialmente para muy-alto-frecuencia usos, por ejemplo radiofrecuenciacircuitos para los sistemas sin hilos. Los transistores bipolares se pueden combinar con los MOSFETs en un circuito integrado usando a BiCMOS proceso para crear los circuitos innovadores que se aprovechan de las mejores características de ambos tipos de transistor.

Sensores de temperatura

Debido a la temperatura sabida y la dependencia actual del voltaje forward-biased de la ensambladura del emisor de base, el BJT se puede utilizar para medir temperatura restando dos voltajes en dos diversas corrientes diagonales en un cociente sabido.

Convertidores logarítmicos

Puesto que el voltaje del emisor de base varía como el registro de las corrientes del emisor de base y del collector-emitter, un BJT se puede también utilizar para computar logaritmos y antilogaritmos. Un diodo puede también realizar estas funciones no lineales, pero el transistor proporciona más flexibilidad del circuito.

Vulnerabilidades

Exposición del transistor a radiación de ionización causas daños de la radiación. La radiación causa una acumulación de los "defectos" en la región baja que actúan como centros de la recombinación. La reducción que resulta en curso de la vida del portador de la minoría causa la pérdida gradual de aumento del transistor. La energía BJTs está conforme a un modo de fallo llamado interrupción secundaria. En este modo de fallo, ciertas partes del dado (el pedazo real de silicio dentro del dispositivo) consiguen más calientes que las otras. Consecuentemente, la parte más caliente del dado conduce más la corriente que lo hace conseguir un alambique más caliente hasta que el dispositivo cortocircuitos internamente.

Freddy Vallenilla CAF