Negative feedback amplifier

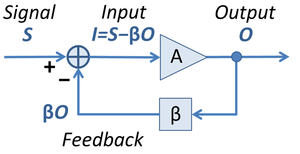

When a fraction of the output of an amplifier is combined with the input, feedback exists; if the feedback opposes the original signal, it is negative feedback and if it increases the signal it is positive feedback. A negative feedback amplifier, or more commonly simply a feedback amplifier, is an amplifier which uses negative feedback to improve performance (gain stability, linearity, frequency response, step response) and reduce sensitivity to parameter variations due to manufacturing or environmental uncertainties. A single feedback loop with unilateral blocks is shown in Figure 1. Negative feedback is used in this way in many amplifiers and control systems.

Figure 1: Ideal negative feedback model

Classical feedback

Voltage amplifiers

Below, the gain of the amplifier with feedback, the closed-loop gain Afb, is derived in terms of the gain of the amplifier without feedback, the open-loop gain AOL and the feedback factor β, which governs how much of the output signal is applied to the input. See Figure 1, top right. The feedback parameter β is determined by the feedback network that is connected around the amplifier. For an operational amplifier two resistors may be used for the feedback network to set β between 0 and 1. This network may be modified using reactive elements like capacitors or inductors to (a) give frequency-dependent closed-loop gain as in equalization/tone-control circuits or (b) construct oscillators.Consider a voltage amplifier with voltage feedback. Without feedback, the output voltage Vout = AOL Vin, where the open-loop gain AOL in general may be a function of both frequency and voltage. The open-loop gain AOL is defined by:

Suppose we have a feedback loop so that a fraction β Vout of the output is subtracted from the input. The input to the amplifier is now V'in, where

,

,

The combination L = β AOL appears commonly in feedback analysis and is called the loop gain. The combination ( 1 + β AOL ) also appears commonly and is variously named as the desensitivity factor or the improvement factor.

Bandwidth extension

Feedback can be used to extend the bandwidth of an amplifier (speed it up) at the cost of lowering the amplifier gain. Figure 2 shows such a comparison. The figure is understood as follows. Without feedback the so-called open-loop gain in this example has a single time constant frequency response given by

The last expression shows the feedback amplifier still has a single time constant behavior, but the corner frequency is now increased by the improvement factor ( 1 + β A0 ), and the gain at zero frequency has dropped by exactly the same factor. This behavior is called the gain-bandwidth tradeoff. In Figure 2, ( 1 + β A0 ) = 103, so Afb(0)= 105 / 103 = 100 V/V, and fC increases to 104 × 103 = 107 Hz.

Multiple poles

When the open-loop gain has several poles, rather than the single pole of the above example, feedback can result in complex poles (real and imaginary parts). In a two-pole case, the result is peaking in the frequency response of the feedback amplifier near its corner frequency, and ringing and overshoot in its step response. In the case of more than two poles, the feedback amplifier can become unstable, and oscillate. See the discussion of gain margin and phase margin. For a complete discussion, see Sansen.Feedback and amplifier type

Amplifiers use current or voltage as input and output, so four types of amplifier are possible. See classification of amplifiers. Any of these four choices may be the open-loop amplifier used to construct the feedback amplifier. The objective for the feedback amplifier also may be any one of the four types of amplifier, not necessarily the same type as the open-loop amplifier. For example, an op amp (voltage amplifier) can be arranged to make a current amplifier instead. The conversion from one type to another is implemented using different feedback connections, usually referred to as series or shunt (parallel) connections. See the table below.

The feedback can be implemented using a two-port network. There are four types of two-port network, and the selection depends upon the type of feedback. For example, for a current feedback amplifier, current at the output is sampled and combined with current at the input. Therefore, the feedback ideally is performed using an (output) current-controlled current source (CCCS), and its imperfect realization using a two-port network also must incorporate a CCCS, that is, the appropriate choice for feedback network is a g-parameter two-port.

Two-port analysis of feedback

One approach to feedback is the use of return ratio. Here an alternative method used in most textbooks is presented by means of an example treated in the article on asymptotic gain model.Figure 3 shows a two-transistor amplifier with a feedback resistor Rf. The aim is to analyze this circuit to find three items: the gain, the output impedance looking into the amplifier from the load, and the input impedance looking into the amplifier from the source.

Replacement of the feedback network with a two-port

The first step is replacement of the feedback network by a two-port. Just what components go into the two-port?On the input side of the two-port we have Rf. If the voltage at the right side of Rf changes, it changes the current in Rf that is subtracted from the current entering the base of the input transistor. That is, the input side of the two-port is a dependent current source controlled by the voltage at the top of resistor R2.

One might say the second stage of the amplifier is just a voltage follower, transmitting the voltage at the collector of the input transistor to the top of R2. That is, the monitored output signal is really the voltage at the collector of the input transistor. That view is legitimate, but then the voltage follower stage becomes part of the feedback network. That makes analysis of feedback more complicated.

An alternative view is that the voltage at the top of R2 is set by the emitter current of the output transistor. That view leads to an entirely passive feedback network made up of R2 and Rf. The variable controlling the feedback is the emitter current, so the feedback is a current-controlled current source (CCCS). We search through the four available two-port networks and find the only one with a CCCS is the g-parameter two-port, shown in Figure 4. The next task is to select the g-parameters so that the two-port of Figure 4 is electrically equivalent to the L-section made up of R2 and Rf. That selection is an algebraic procedure made most simply by looking at two individual cases: the case with V1 = 0, which makes the VCVS on the right side of the two-port a short-circuit; and the case with I2 = 0. which makes the CCCS on the left side an open circuit. The algebra in these two cases is simple, much easier than solving for all variables at once. The choice of g-parameters that make the two-port and the L-section behave the same way are shown in the table below.

http://en.wikipedia.org/wiki/Negative_feedback_amplifier

Rooselvet Ramirez EES